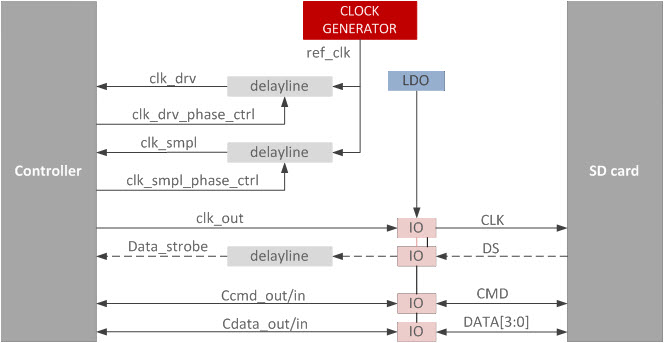

The SD/EMMC PHY IP supports up to 208MHz which compliant with SDIO and EMMC specification. The SDIO/EMMC PHY includes DLL/Delay lines and IO. I/O input voltage is 3.3V, and signal voltage is within 3.3V/1.8V. Delay line supports dual data rate for DDR50, and single data rate for SDR104.

The DLL/Delay lines in SD/EMMC PHY IP support fine resolution, and the IP support bypass mode to control the delay lines.

|

|

|