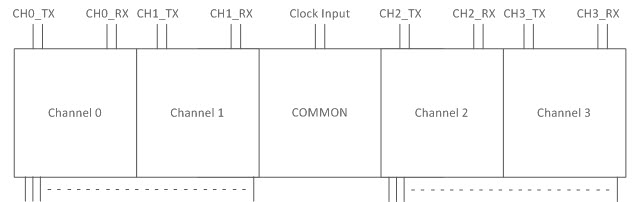

This 1-lane to 4-lane PCIE PHY includes all high-speed analog functions for high-speed data transport between chips over PCBs and high quality cables. It can support different data rates (2.5Gbps to 8Gbps) for compatible with PCIe1.1, PCIe2.1 and PCIe3.1 protocols. It is optimized for low power operation and is suitable for 8b, 10b, 16b, 20b input data path width.

For long trace signal transmission, the PCIe PHY contains programmable 3-tap FFE, CTLE and 5-tap DFE with adaptive algorithm. In-built Eye Monitor can help analysis internal high-speed signal and BIST function is useful for production test.

|

| |