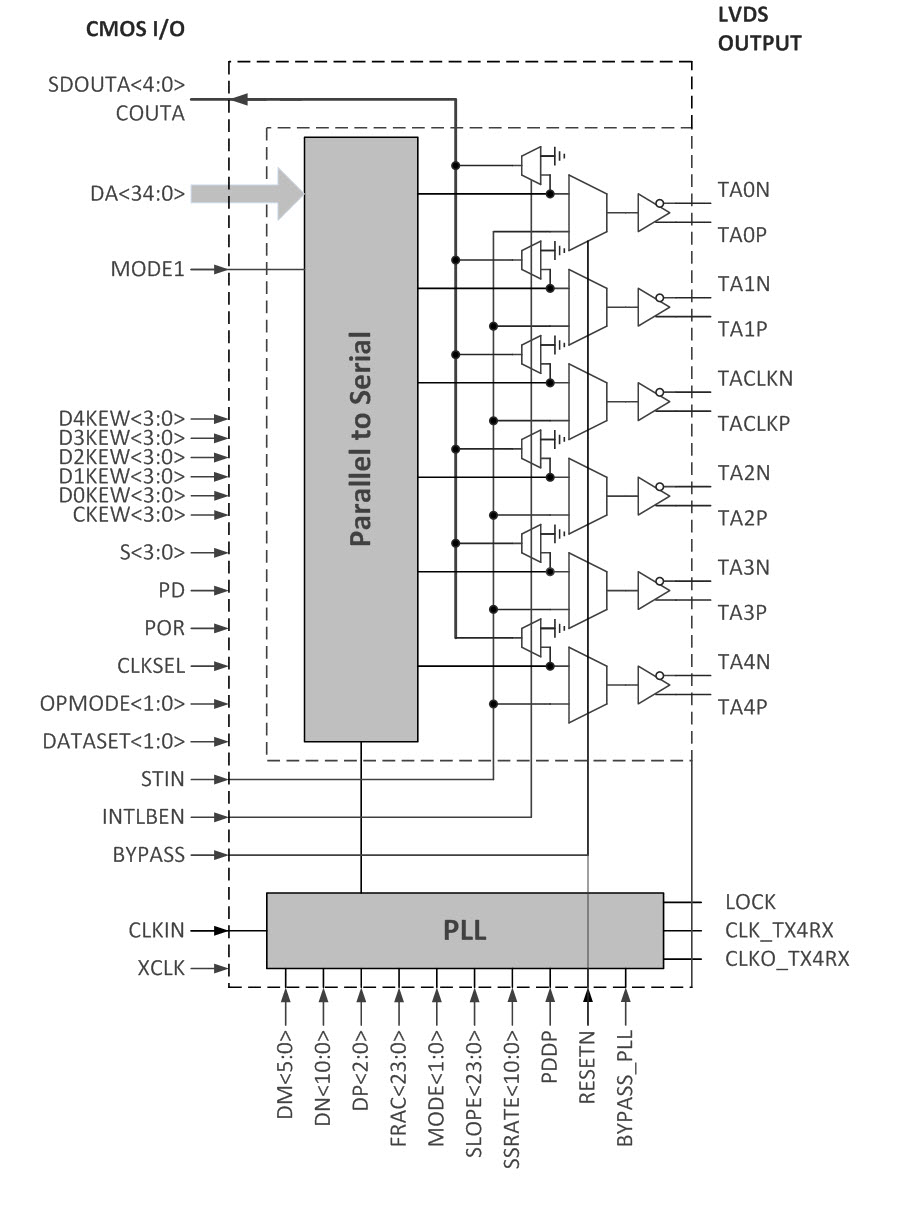

The LVDS transmitter is designed to support Single Link transmission between Host and Flat Panel Display with up to SXGA+ resolution and Dual Link transmission between Host and Flat Panel Display with up to UXGA resolution.

The IP converts 35-bit of CMOS/TTL data into LVDS data stream. The transmitter can be programmed for rising edge or falling edge clocks via a dedicated pin.

|

|

|