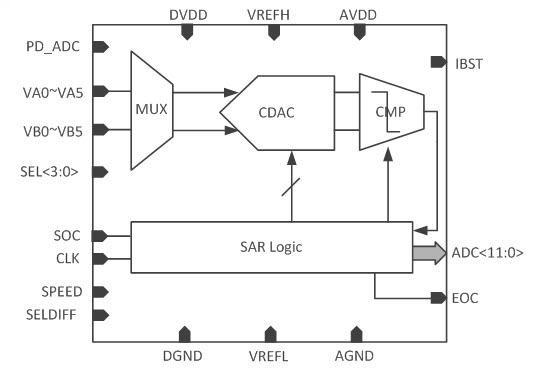

This analog-to-digital converter uses Successive Approximation Register (SAR) architecture to achieve 12-bit resolution.

This ADC has dual input modes, i.e. single-ended and differential-ended. Differential-ended mode is used in noisy environment; whereas single-ended mode is used in clean environment. In single-ended input mode, 12 channels’ input signals can be selected. In differential-ended input mode, 6 pairs’ differential input signals can be selected.

The ADC has dual speed modes – 1Msps or 200Ksps, working in 200K mode could save some power.

It is suitable for integrated auxiliary codec applications and multi-converter architectures in wireless or battery-operated products.

|

|

|