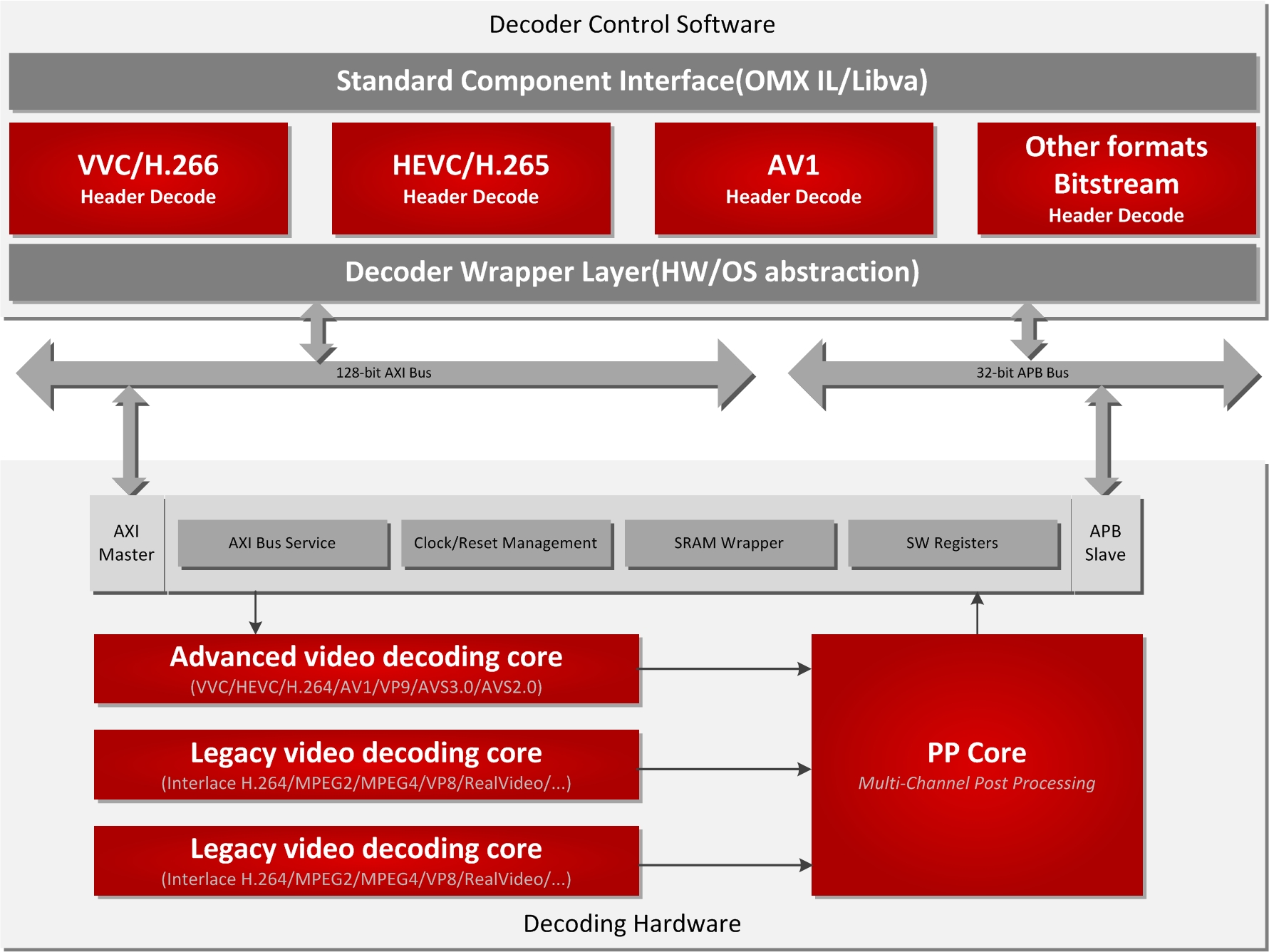

VeriSilicon's Hantro VC9800D enables up to 256 streams decoding with robustness, high throughput single-core solution, or multi-core solution, supporting VVC, AV1, HEVC, H.264, AVS3, AVS2, VP9 video formats, JPEG, and legacy formats.

VeriSilicon's Hantro is based on silicon-proven VeriSilicon Hantro technology and target to demand the high number steams, high throughput, low bandwidth data centers to address the video transcoding, AI server, desktop virtualization even cloud gaming applications.

Hantro VC9800D provides semiconductor manufacturers a minimum risk solution for integrating high-performance video capability into their chips.

VeriSilicon operates globally and we are happy to meet you at any time to discuss your order demand for Hantro VC9800D.

Please feel free to contact us and submit your request online, or reach out to your nearest VeriSilicon sales office for making an order or appointment, or meet us at the next industry event.