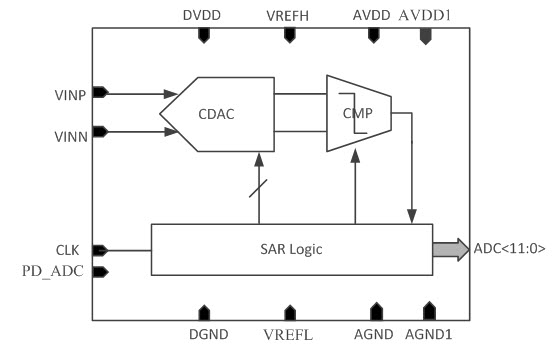

The analog-to-digital converter is a differential high speed low power IP which uses Successive Approximation Register (SAR) architecture to achieve 12-bit resolution. The ADC includes a core internal SAR ADC which consists of sample/hold circuits, a capacitive DAC, a comparator and logic control circuits.

The ADC is designed with high dynamic performance for input signal frequencies up to Nyquist.

It is perfectly suitable for broadband communication applications.

|

|

|