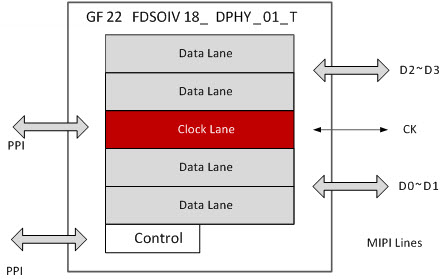

This is a DPHY IP compliant to the “MIPI Alliance Spec for D-PHY v1.1/v1.2”, which consists of Bi-directional 1-Clock and 4-Data lanes. It can support both Master and Slave side. Each lane supports 2.5Gbps in High-Speed mode and 10Mbps/lane in Low-Power escape mode. The target applications are CSI-2 and DSI physical layers.

|

| |