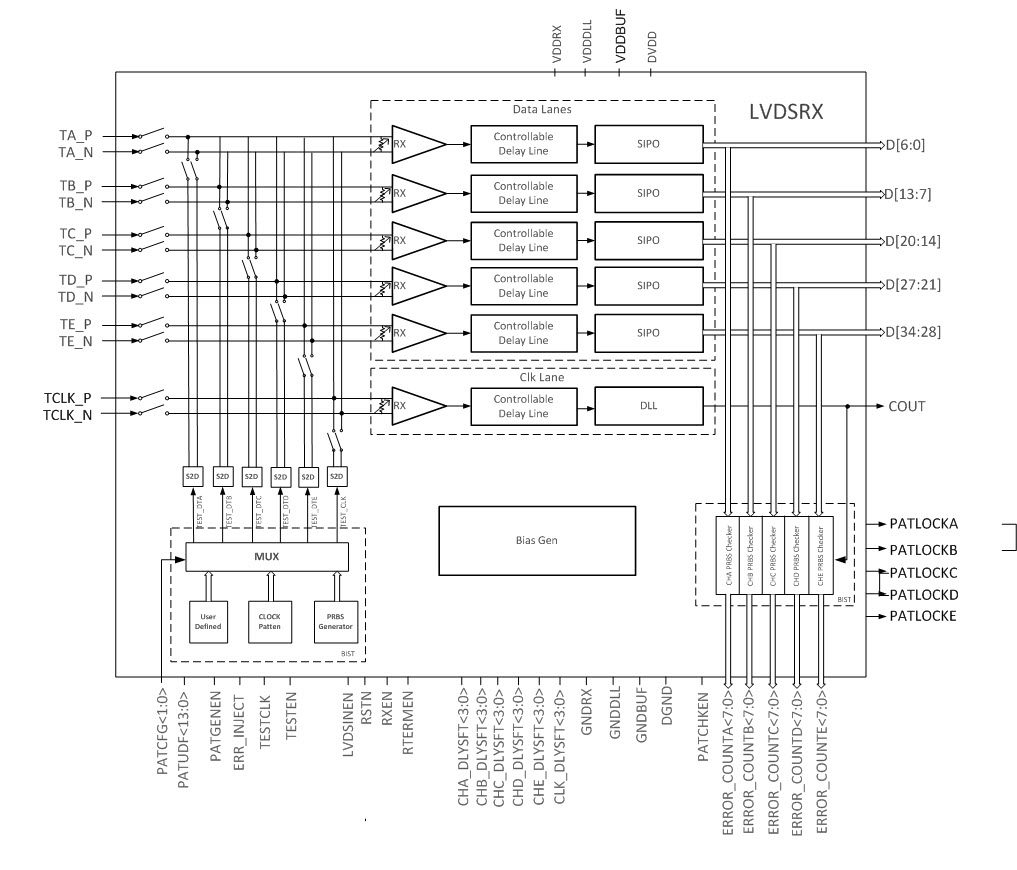

The LVDS Receiver IP is designed to support Single Link transmission between Host and Flat Panel Display with up to SXGA+ resolution. The LVDS Receiver IP converts the LVDS data stream back into 35 bits of CMOS data with a variety of LCD panel controllers.

The receiver LVDS clock operates at rates from 25 MHz to 150 MHz, At an incoming clock rate of 150MHz, each LVDS input line is running at a bit rate of 1.05Gbps.

|

|

|