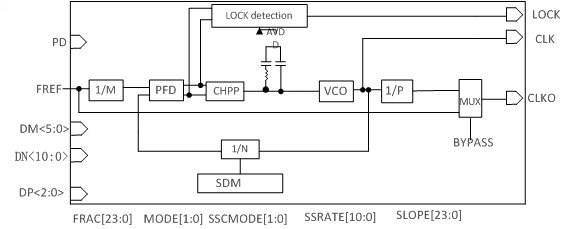

This PLL IP is a programmable Analog PLL suitable for high speed clock generation. The high speed VCO can run from 800MHz to 3200MHz. By proper configurations to different values according to different FREF, CLK will be locked at the multiples of input frequency. CLKO is CLK divided by DP.

The output clock has excellent jitter performance, and can be used as high speed clock generator in SoCs and provide clock for high accuracy ADC converters.

|

|

|